# M1200 Interface Modul

**Technische Beschreibung**

Eiserstraße 5 Telefon 05246/709-0 D-33415 Verl Telefax 05246/70980

Datum : **16.2.94** Version : **2.0** Seite **1** von 15

## Inhaltsverzeichnis

| 1. Funktionsbeschreibung Hardware | 3 |

|-----------------------------------|---|

| 2. Funktionsbeschreibung Software | 5 |

| 3. Technische Daten               | 6 |

| 4. Installationshinweise          | 7 |

| 5. Anschlußplan                   | 9 |

## 1. Funktionsbeschreibung Hardware

M1200

#### **Allgemeines**

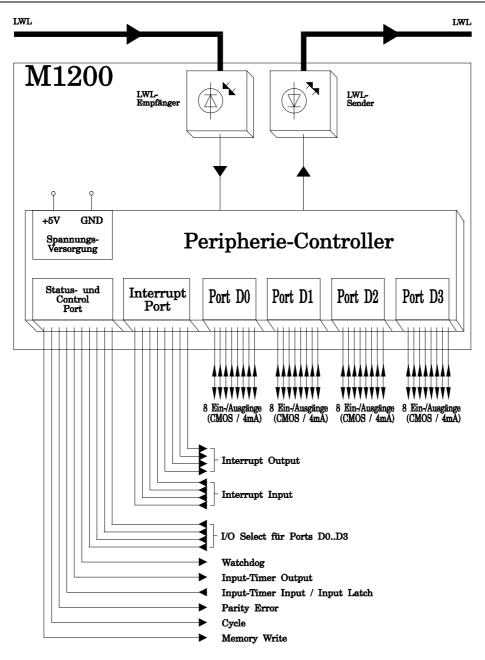

Das Interface Modul M1200 ermöglicht den Anschluß kunden-spezifischer Peripherie-Elektronik an das Lichtleiter II/O-System. 32 parallele Daten Ein-/Ausgänge, 4 "schnelle" Interrupts, sowie Interface Control Signale ermöglichen eine einfache Anpassung an verschiedenste Anwendungen. Über den Lichtleiteranschluß des II/O-Systems erfolgt eine schnelle störsichere Datenübertragung zu einem Zentralgerät wie PC, SPS oder CNC.

Datum: **16.2.94** Version: **2.0** Seite **3** von 15

**Blockschaltbild**

Seite 4 von 15 Version : 2.0 Datum : 16.2.94

## 2. Funktionsbeschreibung Software

Die Ports D0 .. D3 entsprechen den Datenbytes im LWL-Übertragungsprotokoll, und sind je nach Anwendung als Ein- oder Ausgänge konfigurierbar.

Datum : **16.2.94** Version : **2.0** Seite **5** von 15

# 3. Technische Daten

| Ein-/Ausgänge         | 4 Parallel-Ports (8Bit)<br>4 Interrupts (25µs Auflösung)     |

|-----------------------|--------------------------------------------------------------|

| Steuersignale         | Data Read, Data Write, I/O Select,<br>Cycle, Error, Watchdog |

| Eingangsspezifikation | CMOS                                                         |

| Ausgangsspezifikation | CMOS, $I_{out} = 4 \text{ mA}$                               |

| Ausgangsüberwachung   | Watchdog-Schaltung (100ms)                                   |

| Datenanschluß         | Lichtleiter II/O-System                                      |

| Übertragungsrate      | 2,5 MBaud, 25µs für 32 Bit                                   |

| Versorgungsspannung   | 5 VDC (±5%)                                                  |

| Stromaufnahme         | 0,15 A (ohne Last- und Eingangsströme)                       |

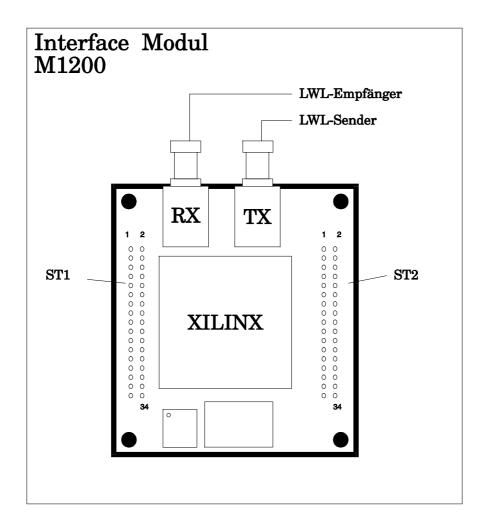

| Anschlüsse            | steckbar (2 * 34 polige Steckerleiste)                       |

| Gehäuseform           | Print-Karte für Steck- oder Schraubmontage                   |

| Abmessungen (B*H*T)   | 63 * 72 * 20 mm                                              |

| Gewicht               | ca. 100 g                                                    |

| Betriebstemperatur    | ±0+55 °C                                                     |

| Lagertemperatur       | -20+70 °C                                                    |

Seite 6 von 15 Version : 2.0 Datum : 16.2.94

### 4. Installationshinweise

Das M1200 wird mit LWL Steckverbindern (Toshiba) an den II/O Lichtleiterring angeschlossen. Die maximale LWL-Kabellänge bis zu den Nachbarboxen sollte 45m bei Kunststofflichtleitern und 600m bei Glasfaser nicht übersteigen. Diese Werte gelten nur, wenn beim Verlegen der LWL-Kabel Biegeradien von min. 30 mm eingehalten werden. Bei Verwendung von Kunststofflichtleitern ist zur Montage der Stecker kein Spezialwerkzeug erforderlich.

Die 5V Versorgungsspannung muß über den 34 poligen Stecker angeschlossen werden.

Datum: **16.2.94** Version: **2.0** Seite **7** von 15

Technische Modulskizze

Seite 8 von 15 Version : 2.0 Datum : 16.2.94

# 5. Anschlußplan

### Steckeranschlußbelegung mit Signalbeschreibung

### STECKER ST1

| Stecker | Pin | Signal                                         | Beschreibung                                                                      |

|---------|-----|------------------------------------------------|-----------------------------------------------------------------------------------|

| ST1     | 1   | +5V                                            | +5VDC Hilfsspannung, Imax = 0,3 A                                                 |

| ST1     | 2   | GND                                            | GND Spannungsversorgung                                                           |

| ST1     | 3   | D0.7                                           | Bit 7 des Datenbyte 0                                                             |

|         |     |                                                | D0.7 ist Output, wenn I/O-Select $S0 = 0$                                         |

|         |     |                                                | D0.7 ist Input, wenn I/O-Select S0 = 1                                            |

| ST1     | 4   | D0.6                                           | Bit 6 des Datenbyte 0                                                             |

|         |     |                                                | D0.6 ist Output, wenn I/O-Select $S0 = 0$                                         |

|         |     |                                                | D0.6 ist Input, wenn I/O-Select S0 = 1                                            |

| ST1     | 5   | D0.5                                           | Bit 5 des Datenbyte 0                                                             |

|         |     |                                                | D0.5 ist Output, wenn I/O-Select $S0 = 0$                                         |

|         |     |                                                | D0.5 ist Input, wenn I/O-Select S0 = 1                                            |

| ST1     | 6   | D0.4                                           | Bit 4 des Datenbyte 0                                                             |

|         |     |                                                | D0.4 ist Output, wenn I/O-Select $S0 = 0$                                         |

|         |     |                                                | D0.4 ist Input, wenn I/O-Select S0 = 1                                            |

| ST1     | 7   | D0.3                                           | Bit 3 des Datenbyte 0                                                             |

|         |     |                                                | D0.3 ist Output, wenn I/O-Select S0 = 0                                           |

|         |     |                                                | D0.3 ist Input, wenn I/O-Select S0 = 1                                            |

| ST1     | 8   | D0.2                                           | Bit 2 des Datenbyte 0                                                             |

|         |     |                                                | D0.2 ist Output, wenn I/O-Select $S0 = 0$                                         |

|         | _   |                                                | D0.2 ist Input, wenn I/O-Select S0 = 1                                            |

| ST1     | 9   | D0.1                                           | Bit 1 des Datenbyte 0                                                             |

|         |     |                                                | D0.1 ist Output, wenn I/O-Select $S0 = 0$                                         |

| ~=1     | 1.0 | 700                                            | D0.1 ist Input, wenn I/O-Select S0 = 1                                            |

| ST1     | 10  | D0.0                                           | Bit 0 des Datenbyte 0                                                             |

|         |     |                                                | D0.0 ist Output, wenn I/O-Select S0 = 0                                           |

| C/D1    | 1.1 | D1.7                                           | D0.0 ist Input, wenn I/O-Select S0 = 1                                            |

| ST1     | 11  | D1.7                                           | Bit 7 des Datenbyte 1                                                             |

|         |     |                                                | D1.7 ist Output, wenn I/O-Select S1 = 0<br>D1.7 ist Input, wenn I/O-Select S1 = 1 |

| C/T/1   | 10  | D1.6                                           | Bit 6 des Datenbyte 1                                                             |

| ST1     | 12  | D1.6                                           | D1.6 ist Output, wenn I/O-Select S1 = 0                                           |

|         |     |                                                | D1.6 ist Input, wenn I/O-Select S1 = 0                                            |

| ST1     | 13  | D1.5                                           | Bit 5 des Datenbyte 1                                                             |

| 511     | 13  | ו.ט                                            | D1.5 ist Output, wenn I/O-Select $S1 = 0$                                         |

|         |     |                                                | D1.5 ist Output, wenn I/O-Select S1 = 0  D1.5 ist Input, wenn I/O-Select S1 = 1   |

| ST1     | 14  | D1.4                                           | Bit 4 des Datenbyte 1                                                             |

| 311     | 14  | D1.4                                           | D1.4 ist Output, wenn I/O-Select S1 = $0$                                         |

|         |     |                                                | D1.4 ist Input, wenn I/O-Select S1 = 0                                            |

| L       | I   | <u>i                                      </u> | 21. 1 lot input, well 1/0 beloet b1 - 1                                           |

Datum : **16.2.94** Version : **2.0** Seite **9** von 15

#### Fortsetzung Stecker ST1:

|      | T              | 1    |                                                |

|------|----------------|------|------------------------------------------------|

| ST1  | 15             | D1.3 | Bit 3 des Datenbyte 1                          |

|      |                |      | D1.3 ist Output, wenn I/O-Select $S1 = 0$      |

|      |                |      | D1.3 ist Input, wenn I/O-Select $S1 = 1$       |

| ST1  | 16             | D1.2 | Bit 2 des Datenbyte 1                          |

|      | 10             | 21.2 | D1.2 ist Output, wenn I/O-Select S1 = $0$      |

|      |                |      | D1.2 ist Input, wenn I/O-Select S1 = 1         |

| ST1  | 17             | D1.1 | Bit 1 des Datenbyte 1                          |

| 311  | 1 /            | D1.1 | D1.1 ist Output, wenn I/O-Select $S1 = 0$      |

|      |                |      | =                                              |

| GTI1 | 10             | D1.0 | D1.1 ist Input, wenn I/O-Select S1 = 1         |

| ST1  | 18             | D1.0 | Bit 0 des Datenbyte 1                          |

|      |                |      | D1.0 ist Output, wenn I/O-Select $S1 = 0$      |

|      |                |      | D1.0 ist Input, wenn I/O-Select S1 = 1         |

| ST1  | 19             | IIO  | Interrupt-Input 0                              |

|      |                |      | Das Interrupt-Bit I0 eines durchlaufenden      |

|      |                |      | Telegrammes wird mit dem logischen Wert des    |

|      |                |      | Interrupt-Inputs II0 verodert. ("Wired-Or" der |

|      |                |      | II0-Eingänge über alle Module, pos. Logik)     |

| ST1  | 20             | II1  | Interrupt-Input 1                              |

| 511  | 20             | 111  | Das Interrupt-Bit I1 eines durchlaufenden      |

|      |                |      | Telegrammes wird mit dem logischen Wert des    |

|      |                |      | Interrupt-Inputs II1 verodert. ("Wired-Or" der |

|      |                |      |                                                |

| C/D1 | 21             | TTO  | III-Eingänge über alle Module, pos. Logik)     |

| ST1  | 21             | II2  | Interrupt-Input 2                              |

|      |                |      | Das Interrupt-Bit I2 eines durchlaufenden      |

|      |                |      | Telegrammes wird mit dem logischen Wert des    |

|      |                |      | Interrupt-Inputs II2 verodert. ("Wired-Or" der |

|      |                |      | II2-Eingänge über alle Module, pos. Logik)     |

| ST1  | 22             | II3  | Interrupt-Input 3                              |

|      |                |      | Das Interrupt-Bit I3 eines durchlaufenden      |

|      |                |      | Telegrammes wird mit dem logischen Wert des    |

|      |                |      | Interrupt-Inputs II3 verodert. ("Wired-Or" der |

|      |                |      | II3-Eingänge über alle Module, pos. Logik)     |

| ST1  | 23             | IO0  | Interrupt-Output 0                             |

|      | 23             | 100  | Der logische Wert des Interrupt Bit I0 eines   |

|      |                |      | durchlaufenden Telegrammes wird auf dem        |

|      |                |      | Output IO0 ausgegeben (pos. Logik)             |

| CT1  | 24             | IO1  | Interrupt-Output 1                             |

| ST1  | ∠ <del>4</del> | 101  | Der logische Wert des Interrupt Bit I1 eines   |

|      |                |      |                                                |

|      |                |      | durchlaufenden Telegrammes wird auf dem        |

| GE 4 | 2.7            | 102  | Output IO1 ausgegeben (pos. Logik)             |

| ST1  | 25             | IO2  | Interrupt-Output 2                             |

|      |                |      | Der logische Wert des Interrupt Bit I2 eines   |

|      |                |      | durchlaufenden Telegrammes wird auf dem        |

|      |                |      | Output IO2 ausgegeben pos. Logik               |

| ST1  | 26             | IO3  | Interrupt-Output 3                             |

|      |                |      | Der logische Wert des Interrupt Bit I3.eines   |

|      |                |      | durchlaufenden Telegrammes wird auf dem        |

|      |                |      | Output IO3 ausgegeben (pos. Logik)             |

| ST1  | 27             |      | n.c.                                           |

|      |                |      |                                                |

| ST1  | 28             |      | n.c.                                           |

Fortsetzung Stecker ST1:

Fortsetzung Stecker ST1:

Seite 10 von 15 Version : 2.0 Datum : 16.2.94

| ST1 | 29 | p38 | Pin 38 des XILINX LCA: |

|-----|----|-----|------------------------|

|     |    |     | reserviert             |

| ST1 | 30 | p41 | Pin 41 des XILINX LCA: |

|     |    | _   | reserviert             |

| ST1 | 31 | p45 | Pin 45 des XILINX LCA: |

|     |    | _   | reserviert             |

| ST1 | 32 |     | n.c.                   |

| ST1 | 33 |     | n.c.                   |

| ST1 | 34 |     | n.c.                   |

## STECKER ST2

| Stecker | Pin | Signal | Beschreibung                                                                                                                                                                                                                                                                                                              |

|---------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ST2     | 1   | +5V    | +5VDC Hilfsspannung, Imax = 0,3 A                                                                                                                                                                                                                                                                                         |

| ST2     | 2   | GND    | GND Spannungsversorgung                                                                                                                                                                                                                                                                                                   |

| ST2     | 3   | D3.7   | Bit 7 des Datenbyte 3 D3.7 ist Output, wenn I/O-Select S3 = 0 D3.7 ist Input, wenn I/O-Select S3 = 1                                                                                                                                                                                                                      |

| ST2     | 4   | D3.6   | Bit 6 des Datenbyte 3 D3.6 ist Output, wenn I/O-Select S3 = 0 D3.6 ist Input, wenn I/O-Select S3 = 1  **Anmerkung** D3.6 wird auch als Dateneingang für die XILINX-Konfiguration verwendet. D3.6 darf daher nur über einen Serien-Widerstand von 10kOhm mit einer externen Schaltung verbunden werden, sonst 1 x TTL-Last |

| ST2     | 5   | D3.5   | Bit 5 des Datenbyte 3 D3.5 ist Output, wenn I/O-Select S3 = 0 D3.5 ist Input, wenn I/O-Select S3 = 1                                                                                                                                                                                                                      |

| ST2     | 6   | D3.4   | Bit 4 des Datenbyte 3 D3.4 ist Output, wenn I/O-Select S3 = 0 D3.4 ist Input, wenn I/O-Select S3 = 1                                                                                                                                                                                                                      |

| ST2     | 7   | D3.3   | Bit 3 des Datenbyte 3 D3.3 ist Output, wenn I/O-Select S3 = 0 D3.3 ist Input, wenn I/O-Select S3 = 1                                                                                                                                                                                                                      |

| ST2     | 8   | D3.2   | Bit 2 des Datenbyte 3 D3.2 ist Output, wenn I/O-Select S3 = 0 D3.2 ist Input, wenn I/O-Select S3 = 1                                                                                                                                                                                                                      |

| ST2     | 9   | D3.1   | Bit 1 des Datenbyte 3 D3.1 ist Output, wenn I/O-Select S3 = 0 D3.1 ist Input, wenn I/O-Select S3 = 1                                                                                                                                                                                                                      |

| ST2     | 10  | D3.0   | Bit 0 des Datenbyte 3 D3.1 ist Output, wenn I/O-Select S3 = 0 D3.1 ist Input, wenn I/O-Select S3 = 1                                                                                                                                                                                                                      |

| ST2     | 11  | D2.7   | Bit 7 des Datenbyte 2 D2.7 ist Output, wenn I/O-Select S2 = 0 D2.7 ist Input, wenn I/O-Select S2 = 1                                                                                                                                                                                                                      |

| ST2     | 12  | D2.6   | Bit 6 des Datenbyte 2 D2.6 ist Output, wenn I/O-Select S2 = 0 D2.6 ist Input, wenn I/O-Select S2 = 1                                                                                                                                                                                                                      |

Fortsetzung Stecker ST2:

Datum : **16.2.94** Version : **2.0** Seite **11** von 15

| ST2   | 13              | D2.5 | Bit 5 des Datenbyte 2                                                                 |

|-------|-----------------|------|---------------------------------------------------------------------------------------|

|       |                 |      | D2.5 ist Output, wenn I/O-Select $S2 = 0$                                             |

|       |                 |      | D2.5 ist Input, wenn I/O-Select S2 = 1                                                |

| ST2   | 14              | D2.4 | Bit 4 des Datenbyte 2                                                                 |

| 212   |                 | 22   | D2.4 ist Output, wenn I/O-Select $S2 = 0$                                             |

|       |                 |      | D2.4 ist Input, wenn I/O-Select S2 = 1                                                |

| ST2   | 15              | D2.3 | Bit 3 des Datenbyte 2                                                                 |

| 512   | 13              | D2.3 | D2.3 ist Output, wenn I/O-Select S2 = $0$                                             |

|       |                 |      | D2.3 ist Gutput, wenn I/O-Select $S2 = 0$<br>D2.3 ist Input, wenn I/O-Select $S2 = 1$ |

| CTO   | 1.6             | D2 2 | Bit 2 des Datenbyte 2                                                                 |

| ST2   | 16              | D2.2 |                                                                                       |

|       |                 |      | D2.2 ist Output, wenn I/O-Select S2 = 0                                               |

| GERA. | 4.5             | D0.1 | D2.2 ist Input, wenn I/O-Select S2 = 1                                                |

| ST2   | 17              | D2.1 | Bit 1 des Datenbyte 2                                                                 |

|       |                 |      | D2.1 ist Output, wenn I/O-Select $S2 = 0$                                             |

|       |                 |      | D2.1 ist Input, wenn I/O-Select S2 = 1                                                |

| ST2   | 18              | D2.0 | Bit 0 des Datenbyte 2                                                                 |

|       |                 |      | D2.0 ist Output, wenn I/O-Select $S2 = 0$                                             |

|       |                 |      | D2.0 ist Input, wenn I/O-Select S2 = 1                                                |

| ST2   | 19              | S3   | I/O Select für Datenbyte 3 (D3.0-D3.7)                                                |

|       |                 |      | Wenn S3=0, dann sind D3.0-D3.7 als Output                                             |

|       |                 |      | geschaltet.                                                                           |

|       |                 |      | Wenn S3=1, dann sind D3.0-D3.7 als Input                                              |

|       |                 |      | geschaltet.                                                                           |

| ST2   | 20              | S2   | I/O Select für Datenbyte 2 (D2.0-D2.7)                                                |

| 512   | 20              | 52   | Wenn S2=0, dann sind D2.0-D2.7 als Output                                             |

|       |                 |      | geschaltet.                                                                           |

|       |                 |      | Wenn S2=1, dann sind D2.0-D2.7 als Input                                              |

|       |                 |      | geschaltet.                                                                           |

| ST2   | 21              | S1   | I/O Select für Datenbyte 1 (D1.0-D1.7)                                                |

| 312   | 21              | 51   | · · · · · · · · · · · · · · · · · · ·                                                 |

|       |                 |      | Wenn S1=0, dann sind D1.0-D1.7 als Output                                             |

|       |                 |      | geschaltet.                                                                           |

|       |                 |      | Wenn S1=1, dann sind D1.0-D1.7 als Input                                              |

|       |                 |      | geschaltet.                                                                           |

| ST2   | 22              | S0   | I/O Select für Datenbyte 0 (D0.0-D0.7)                                                |

|       |                 |      | Wenn S0=0, dann sind D0.0-D0.7 als Output                                             |

|       |                 |      | geschaltet.                                                                           |

|       |                 |      | Wenn S0=1, dann sind D0.0-D0.7 als Input                                              |

|       |                 |      | geschaltet.                                                                           |

| ST2   | 23              | WDT  | Trigger-Impuls für externe Watchdog-                                                  |

|       |                 |      | Schaltung:                                                                            |

|       |                 |      | Unmittelbar nachdem                                                                   |

|       |                 |      | a) ein Telegramm vollständig empfangen                                                |

|       |                 |      | wurde,                                                                                |

|       |                 |      | b) das Modul adressiert worden ist,                                                   |

|       |                 |      | c) kein Übertragungsfehler vorliegt                                                   |

|       |                 |      | und ein Schreibzugriff auf das Modul erfolgt                                          |

|       |                 |      | ist, wird ein Impuls logisch "1" ausgegeben.                                          |

| ST2   | 24              | ITO  | Input-Timer-Output                                                                    |

| 312   | ∠ <del>'1</del> | 110  | Spezielles Trigger-Signal für Input_Timer; wird                                       |

|       |                 |      | im Modul M1000 benutzt.                                                               |

| OTTO  | 25              | ITH  |                                                                                       |

| ST2   | 25              | ITI  | Input-Timer-Input/Input Latch                                                         |

|       |                 |      | Bei ITI=1 werden die Eingangsdaten D00-D37                                            |

|       |                 |      | in das Modul eingelesen.                                                              |

|       |                 |      | Bei ITI=0 werden die Eingangsdaten D00-D37                                            |

|       |                 |      | <u>nicht</u> eingelesen.                                                              |

Seite 12 von 15 Version : 2.0 Datum : 16.2.94

### Fortsetzung Stecker ST2:

| 1   |    | I   | T                                              |

|-----|----|-----|------------------------------------------------|

| ST2 | 26 | PAE | Parity Error                                   |

|     |    |     | Das PAE-Signal wird unmittelbar nach dem       |

|     |    |     | vollständigen Empfang eines Telegrammes        |

|     |    |     | erzeugt.                                       |

|     |    |     | Es gilt:                                       |

|     |    |     | PAE = 0, dann CRC o.k.                         |

|     |    |     | PAE = 1, dann CRC fehlerhaft                   |

|     |    |     | Das Signal wird nach erkennen eines            |

|     |    |     | fehlerhaftenTelegrammes (Checksum, Frame)      |

|     |    |     | eingeschaltet und nach dem Durchlaufen drei    |

|     |    |     | aufeinanderfolgender richtiger Telegramme      |

|     |    |     | wieder ausgeschaltet.                          |

| ST2 | 27 | CYC | CYCLE                                          |

|     |    |     | CYCLE wird mit dem Startbit eines jeden        |

|     |    |     | Telegrammeseingeschaltet (auf "1" gesetzt) und |

|     |    |     | mit dem Stopbit wieder ausgeschaltet.          |

| ST2 | 28 | MWR | Memory Write                                   |

|     | _  |     | Das Memory Write Signal (Active Low) wird      |

|     |    |     | eine definierte Zeit nach dem vollständigen    |

|     |    |     | Empfang eines Telegrammes erzeugt, wenn        |

|     |    |     | a) das Write-Control-Bit im Telegramm          |

|     |    |     | gesetzt ist.                                   |

|     |    |     | b) die CRC-Prüfung fehlerfrei war              |

|     |    |     | c) die Ausgaben-Daten stahl anstehen.          |

| ST2 | 29 |     | n.c.                                           |

| ST2 | 30 | P50 | Pin 50 des XILINX LCA:                         |

|     |    |     | reserviert                                     |

| ST2 | 31 | P51 | Pin 51 des XILINX LCA:                         |

|     |    |     | reserviert                                     |

| ST2 | 32 |     | n.c.                                           |

| ST2 | 33 |     | n.c.                                           |

| ST2 | 34 |     | n.c.                                           |

Datum : **16.2.94** Version : **2.0** Seite **13** von 15

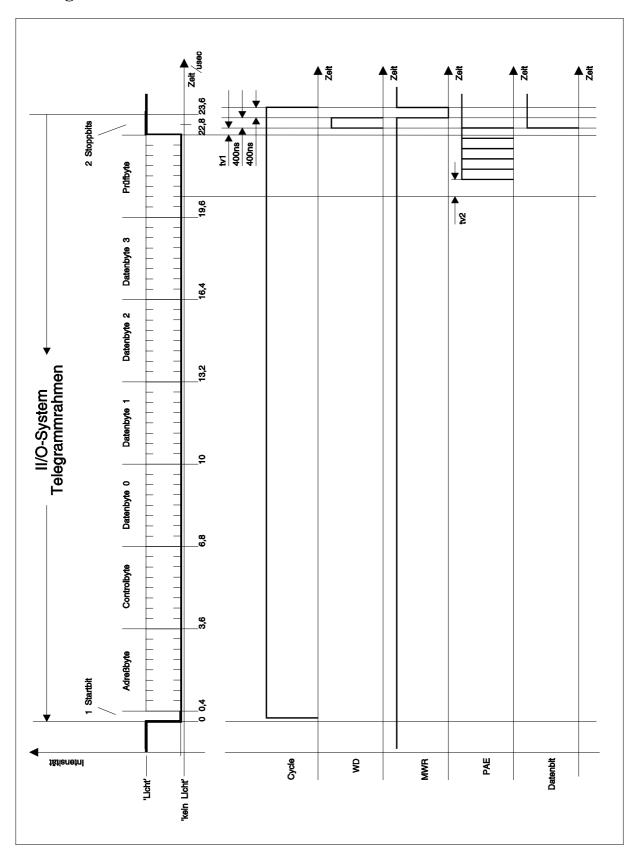

### **Timing**

Timingdiagramm Peripheriecontroller

Seite **14** von 15 Version : **2.0** Datum : **16.2.94**

Im Timing-Diagramm ist die Abhängigkeit zwischen Zeitverlauf des II/O-Telegramm-Rahmens und einigen Peripherie-Controller Signalen dargestellt.

Der II/O-System Telegrammrahmen ist hier als Lichtsignal dargestellt, die weiteren Signale mit ihrem elektrischen Pegel. Die opto-elektronische Wandlung und eine Verzögerung durch logische Gatter im Peripheriecontroller verursachen die Verzögerungszeit  $\mathbf{t_{v1}}$  (ca. 300 ns). Wird ein Fehler beim CRC-Check festgestellt, erfolgt die Ausgabe des PAE-Signals. Die Verzögerungszeit  $\mathbf{t_{v2}}$  setzt sich aus  $\mathbf{t_{v1}}$  (ca. 300 ns) und einer Zeitdauer ( $\mathbf{n+1}$ )\*400ns zusammen.  $\mathbf{n}$  entspricht hier dem CRC-Bit, welches den Fehler signalisiert (z.B.: CRC-Bit 0 =>  $\mathbf{t_{v2}}$  = 300 ns + (0+1)\*400 ns = 700ns).

Der Bitstrom wird in jedem Peripherie-Modul digital-elektrisch aufbereitet und mit einer Verzögerung von ~2 Bit (800 ns) weitergesendet. Die opto-elektrische Wandlung von Sender und Empfänger über LWL ergibt eine weitere Verzögerung von ~1 Bit (400 ns) pro Peripherie-Modul. Die Summe aller Bitstromverzögerungen ergibt sich etwa aus :

Anzahl der Peripherie-Module \* 1200 ns

Datum: **16.2.94** Version: **2.0** Seite **15** von 15